- Academics

-

Research

-

Centres

- E-Health Research Centre (EHRC)

- Machine Intelligence & Robotics CoE (MINRO)

- Centre for IT & Public Policy (CITAPP)

- Cognitive Computing CoE (CCC)

- Centre for Accessibility in the Global South (CAGS)

- COMET Tech Innovation Hub (NM-ICPS)

- IIITB Innovation Centre

- Modular Open-Source Identity Platform (MOSIP)

-

Labs

- Surgical and Assistive Robotics Lab

- Graphics-Visualization-Computing-Lab

- Web Science Lab

- Multimodal Perception Lab

- Software Engineering Lab

- High Density Electronic Systems Lab

- Networking and Communication Lab

- Remote Sensing, GIS and Spatial Computing Lab

- Indian Knowledge System (IKS) Lab

- Smart City Lab

- Ascend Studio

- Radar Sensing Lab

- CSSMP

- Mahabala Ganaka Labs

- Advanced Wireless Communications Lab

- Speech Lab

- Connected Devices and Wearables Lab

- Outreach

- Publications

- Policy

-

Centres

- Placements

- Campus Life

- Media

- People

- About Us

Assistant Professor & Warden (Women's Hostel)

Education : Ph.D. (IIT Bombay)

News:

Jan 2024:

We got 3 acceptances at the 2024 IEEE International Symposium on Circuits & Systems - ISCAS.

1. Jay Shah, Nanditha Rao: "Hybrid Multi-Tile Vector Systolic Architecture for Accelerating Convolution on FPGAs"

2. Chithambara Moorthii J, Vinay Rayapati, Nanditha Rao , Manan Suri, "VPU-CIM: A 130nm, 33.98 TOPS/W RRAM based Compute-In-Memory Vector Co-Processor"

3. Vinay Rayapati, Ravi Kiran Reddy Gogireddy, Ajay Kumar Gandi, Saketh Gajawada, Gopala Krishna Reddy Sanampudi and Nanditha Rao, "FPGA-based Hardware Software Co-design to Accelerate Brain Tumour Segmentation"

Our team involving Yash Mogal, Asmita Zjigyasu, Nancy Gupta, Shivangi, Jay Shah were among the top 5 teams selected to demo in the VLSID Embedded Systems, Design Contest at Kolkata, Jan 2024. They won a special mention at the event.

Nov 2023: Our collaborative work with the University of Utah was presented: Anubhav Mishra, Nanditha Rao, Ganesh Gore and Xifan Tang, "Architectural Exploration of Heterogeneous FPGAs for Performance Enhancement of ML Benchmarks", APCCAS 2023

Our iMTech student Jahanvi Agrawal successfully completed her MITACS internship at Simon Fraser University.

I am formally now part of the Program Committee for DAC 2024 IP Track!

Oct 2023: Jay Shah and Nanditha Rao "Enhancing Convolution Throughput with Vector Systolic Architecture on FPGA" was accepted to the PACT 2023 Student Research Competition!

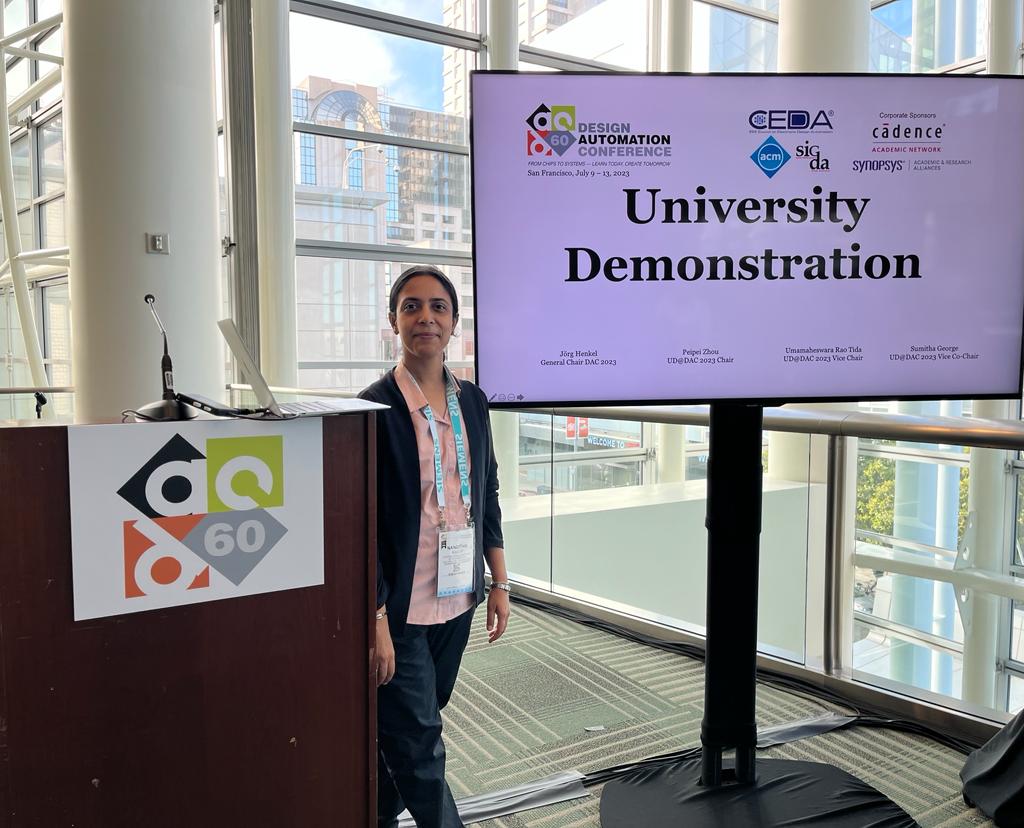

June/July 2023:

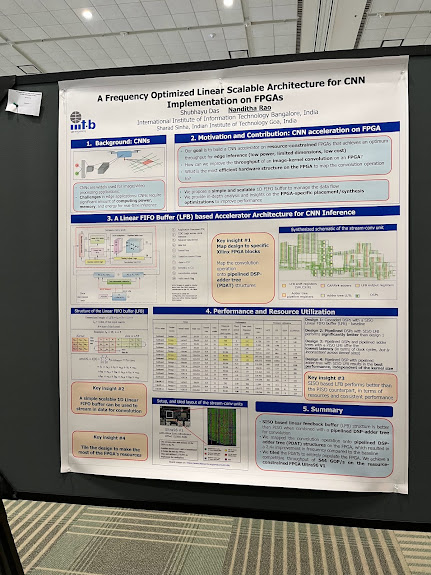

Our work on "A Frequency Optimized Linear Scalable Architecture for CNN Implementation on FPGAs", was accepted for presentation and a poster discussion at the "Advanced IP" track in Design Automation Conference DAC 2023, CA

May 2023: Shivani Shah and Nanditha P Rao, "A Multi-Core Cache Simulator accelerated on a resource-constrained FPGA, GLSVLSI 2023

April 2023: Archie Mishra and Nanditha Rao, "DSEAdd: FPGA based Design Space Exploration for Approximate Adders with Variable Bit-precision", ISQED 2023

March- June 2023: Visiting researcher in the SAFARI research group headed by Prof. Onur Mutlu, ETH Zurich.

Jan 2023

-

We signed an MOU with Infineon for collaboration with my MS(R) student Himanshu. Thanks to the team from Infineon.

- Met a delegation from the UK headed by Dr. Lindy Cameron, CEO of the National Cyber Security Centre visited IIIT Bangalore to understand the institute's contribution to cybersecurity. There were members of the British Deputy High Commission in New Delhi and Bangalore, part of this discussion. Glad to be part of this meet discussing my efforts on hardware security.

- Part of a Faculty Development Program (FDP) to Myanmar Institute of Information Technology (MIIT) through Kunal Ghosh's Vlsi System Design (VSD). I contributed the FPGA component of the FDP.

Dec 2022:

- Our demo on "Hardware software co-design to accelerate brain tumour segmentation and classification" won the first place in the VLSI-D design contest. Our team consists of 4 MTech students: Vinay, Krishna, Ravi and Ajay.

- I was invited to be part of the SERB Core Research Grant Review team

- Our work on "A Frequency Optimized Linear Scalable Architecture for CNN Inference on FPGAs" by: "Shubhayu Das, Nanditha Rao and Sharad Sinha" was presented at VLSI-D User Design Track (UDT) 2023

- Conducted a 5-day workshop on FPGA/OpenFPGA with VSD

- Gave an invited talk at the ICEE conference, Bangalore on "Performance improvement of machine learning hardware accelerators (inference) on FPGA"

- Co-organized the OpenFPGA tutorial, at FPT'2022: International Conference on Field Programmable Technology, We had nearly 120 registrants. It was a great learning experience to set up machines on the cloud, on Digital Ocean.

Nov 2022:

- Our proposal on "Hardware software co-design to accelerate brain tumour segmentation and classification" was selected in the VLSI-D design contest. A Microchip PolarFire FPGA board is being provided to implement our design and demonstrate it at the conference. Our team consists of 4 MTech students: Vinay, Krishna, Ravi and Ajay. The theme of the design contest was "Hardware and Embedded software co-design with hardware acceleration in an SoC FPGA".

- Two of my iMtech students Sai Manish and Rutvi Padhy are interning at Fachhochschule Kärnten in Villach, Austria. They are working on (1) next-generation photonic highspeed chip-to-chip communication and (2) enabling model-based statistical sign-off of critical analog and RF subsystems. They are working with Prof. Johannes Strum and Prof. Wolfgang Scherr (in collaboration with NXP Semiconductors)

Oct 2022:

- Delivered a KeyNote talk at VSDOpen 2022 online conference

- Invited to be part of SERB Core Research Grant review team

Sep 2022:

.jpg)

- Invited to be part of VLSI-D conference TPC for 2 tracks: Hardware for AI and ML, Low power Digital Architectures

- Presented our work at Indian Institute of Astrophysics Soham Das, Nanditha Rao, D.V.S. Phanindra, Rengaswamy Sridharan "FPGA Accelerated Cross Correlation of Digital Images : Application to Solar Adaptive Optics:, Modern Engineering Trends in Astronomy, Sep 2022

- Signed an MOU with Sensonics Devices Private Limited (SDPL) Rajat Gupta, Sanjay Mehta, Nanditha Rao and Subir Roy through which they will fund an MS(R) student tashish Tiwaru to work on a RISC-V co-processor

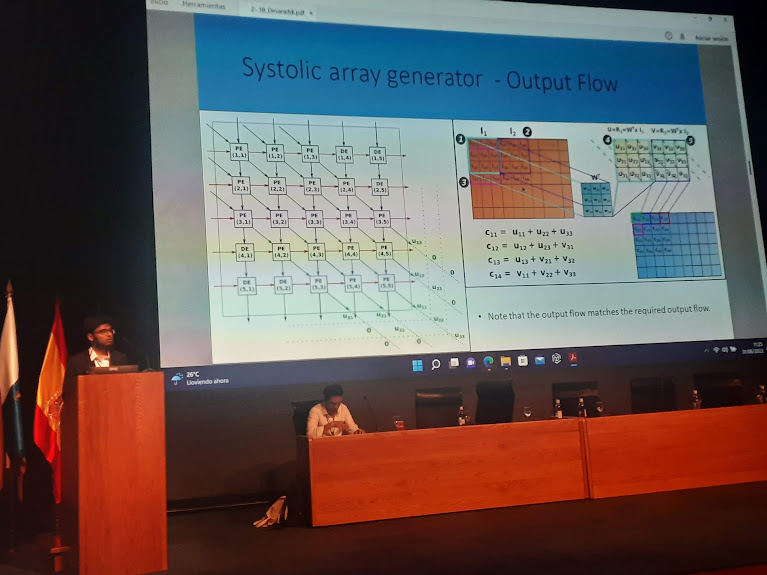

- Our paper was presented in Euromicro Conference on Digital Systems Design 2022. Track: Applications, Architectures, Methods and Tools for Machine – and Deep Learning. Veerendra S Devaraddi and Nanditha Rao, "An FPGA based Tiled Systolic Array Generator to Accelerate CNNs" I was also a session chair for this track

June 2022: Two of my MS(R) students defended their thesis. They are currently placed in Nvidia and Western Digital respectively.

1. Shivani Shah: Cache-accel: FPGA Accelerated Cache Simulator with Partially Reconfigurable Prefetcher

2. Alok Parmar: IMC-Sim: An Architectural Simulator to Benchmark In-Memory Computing in SRAMs (co-advised by Prof. Joycee Mekie, IIT Gandhinagar)

June 2022: Our paper was accepted in Euromicro Conference on Digital Systems Design 2022. Track: Applications, Architectures, Methods and Tools for Machine – and Deep Learning.

Veerendra S Devaraddi and Nanditha Rao, "An FPGA based Tiled Systolic Array Generator to Accelerate CNNs"

June 2022: I conducted a 5-day workshop with VLSI System Design (VSD) on FPGA- Fabric, design and Architecture which covers implementing a RISC-V processor through Xilinx Vivado flow and the OpenFPGA flow (on the Skywater 130nm SOFA eFPGA fabric)

May 2022: Our paper was presented in ISCAS 2022: Alok Parmar, Kailash Prasad, Nanditha Rao, Joycee Mekie, " An Automated Approach to Compare Bit Serial and Bit Parallel In-Memory Computing for DNNs"

Bio:

I completed my PhD from the Department of Electrical Engineering, IIT Bombay, India in 2017 under the supervision of Prof. Madhav Desai. The thesis work focused on studying the impact of single event upsets (soft errors) on digital logic circuits and on FinFET based device layouts. I was awarded the “Institute Organizational Citation” at IIT Bombay. This is awarded to graduating students in recognition of the contribution to institute's organizational activities during the entire stay in the institute.

Prior to joining the PhD programme, I worked as a Hardware design engineer (Signal Integrity) at Intel Technologies, Bangalore for a period of five years. At Intel, I was mainly responsible for signal integrity (SI) simulations of PCIe, LVDS, DisplayPort and HDMI interfaces (entire path from transmitter to package interconnect to motherboard to receiver interconnect). The work involved several motherboard platforms which included processors such as Clarksfield, Sandybridge, Ivybridge and so on. I also reviewed motherboard schematics (laptop segment) of customers and provided design feedback, in addition to developing expertise in IBIS buffer modeling. The work involved cross-geo interactions with Intel Oregon, Penang and Haifa teams. I received 13 Intel ‘spontaneous recognition awards’ and one Intel ‘divisional recognition award’.

My current research interests are in the area of computer architecture and FPGA-based Systems. More specifically the following areas:

- FPGA Acceleration of Neural Networks

- System design using RISC-V based cores

- Exploring FPGA architectures (https://openfpga.readthedocs.io/en/master/overview/motivation/)

- Approximate designs

- Radiation hardened processor cores