- Academics

-

Research

-

Centres

- E-Health Research Centre (EHRC)

- Machine Intelligence & Robotics CoE (MINRO)

- Centre for IT & Public Policy (CITAPP)

- Cognitive Computing CoE (CCC)

- Centre for Accessibility in the Global South (CAGS)

- COMET Tech Innovation Hub (NM-ICPS)

- IIITB Innovation Centre

- Modular Open-Source Identity Platform (MOSIP)

-

Labs

- Surgical and Assistive Robotics Lab

- Graphics-Visualization-Computing-Lab

- Web Science Lab

- Multimodal Perception Lab

- Software Engineering Lab

- High Density Electronic Systems Lab

- Networking and Communication Lab

- Remote Sensing, GIS and Spatial Computing Lab

- Indian Knowledge System (IKS) Lab

- Smart City Lab

- Ascend Studio

- Radar Sensing Lab

- CSSMP

- Mahabala Ganaka Labs

- Advanced Wireless Communications Lab

- Speech Lab

- Connected Devices and Wearables Lab

- Outreach

- Publications

- Policy

-

Centres

- Placements

- Campus Life

- Media

- People

- About Us

Assistant Professor & Warden (Women's Hostel)

Education : Ph.D. (IIT Bombay)

News:

Jan 2024:

We got 3 acceptances at the 2024 IEEE International Symposium on Circuits & Systems - ISCAS.

1. Jay Shah, Nanditha Rao: "Hybrid Multi-Tile Vector Systolic Architecture for Accelerating Convolution on FPGAs"

2. Chithambara Moorthii J, Vinay Rayapati, Nanditha Rao , Manan Suri, "VPU-CIM: A 130nm, 33.98 TOPS/W RRAM based Compute-In-Memory Vector Co-Processor"

3. Vinay Rayapati, Ravi Kiran Reddy Gogireddy, Ajay Kumar Gandi, Saketh Gajawada, Gopala Krishna Reddy Sanampudi and Nanditha Rao, "FPGA-based Hardware Software Co-design to Accelerate Brain Tumour Segmentation"

Our team involving Yash Mogal, Asmita Zjigyasu, Nancy Gupta, Shivangi, Jay Shah were among the top 5 teams selected to demo in the VLSID Embedded Systems, Design Contest at Kolkata, Jan 2024. They won a special mention at the event.

Nov 2023: Our collaborative work with the University of Utah was presented: Anubhav Mishra, Nanditha Rao, Ganesh Gore and Xifan Tang, "Architectural Exploration of Heterogeneous FPGAs for Performance Enhancement of ML Benchmarks", APCCAS 2023

Our iMTech student Jahanvi Agrawal successfully completed her MITACS internship at Simon Fraser University.

I am formally now part of the Program Committee for DAC 2024 IP Track!

Oct 2023: Jay Shah and Nanditha Rao "Enhancing Convolution Throughput with Vector Systolic Architecture on FPGA" was accepted to the PACT 2023 Student Research Competition!

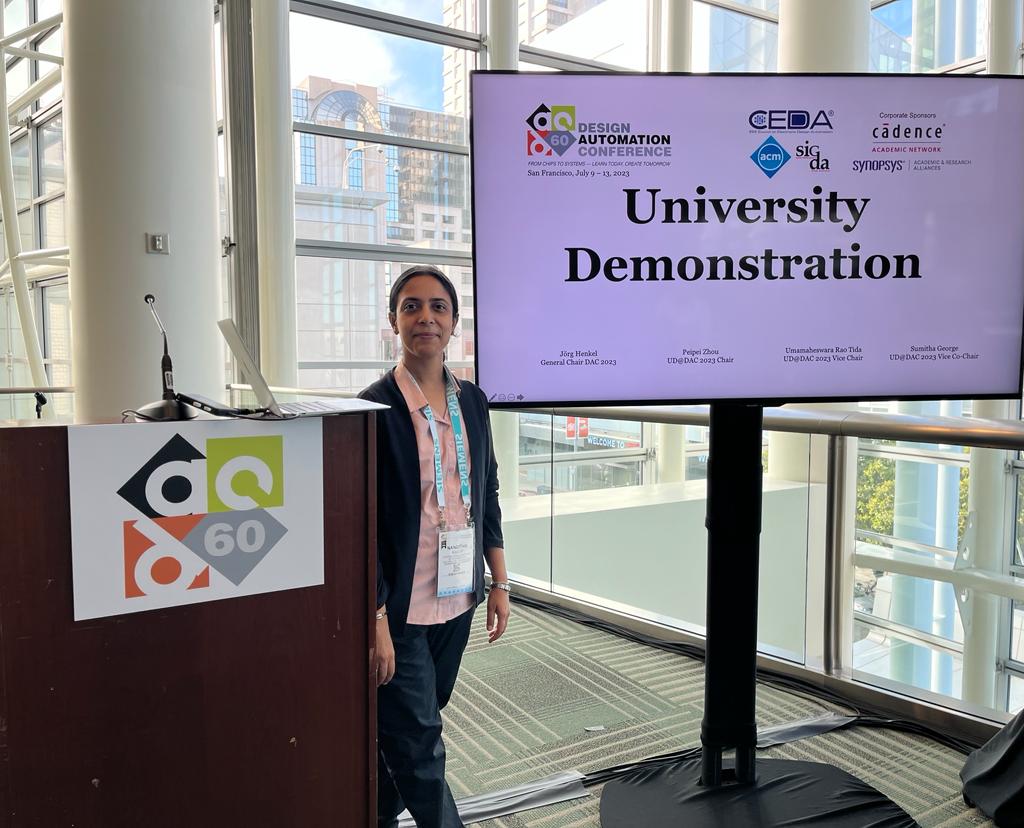

June/July 2023:

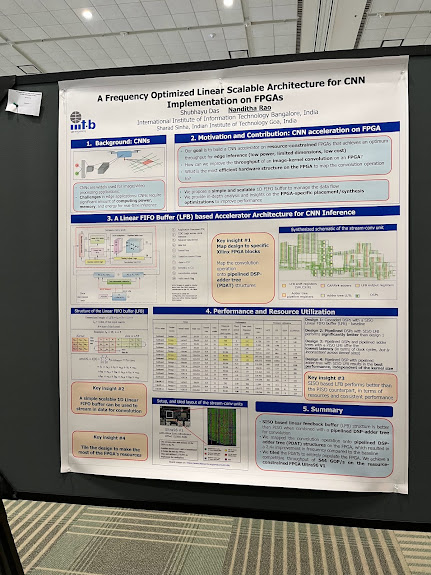

Our work on "A Frequency Optimized Linear Scalable Architecture for CNN Implementation on FPGAs", was accepted for presentation and a poster discussion at the "Advanced IP" track in Design Automation Conference DAC 2023, CA

May 2023: Shivani Shah and Nanditha P Rao, "A Multi-Core Cache Simulator accelerated on a resource-constrained FPGA, GLSVLSI 2023

April 2023: Archie Mishra and Nanditha Rao, "DSEAdd: FPGA based Design Space Exploration for Approximate Adders with Variable Bit-precision", ISQED 2023

March- June 2023: Visiting researcher in the SAFARI research group headed by Prof. Onur Mutlu, ETH Zurich.

Jan 2023

-

We signed an MOU with Infineon for collaboration with my MS(R) student Himanshu. Thanks to the team from Infineon.

- Met a delegation from the UK headed by Dr. Lindy Cameron, CEO of the National Cyber Security Centre visited IIIT Bangalore to understand the institute's contribution to cybersecurity. There were members of the British Deputy High Commission in New Delhi and Bangalore, part of this discussion. Glad to be part of this meet discussing my efforts on hardware security.

- Part of a Faculty Development Program (FDP) to Myanmar Institute of Information Technology (MIIT) through Kunal Ghosh's Vlsi System Design (VSD). I contributed the FPGA component of the FDP.

Dec 2022:

- Our demo on "Hardware software co-design to accelerate brain tumour segmentation and classification" won the first place in the VLSI-D design contest. Our team consists of 4 MTech students: Vinay, Krishna, Ravi and Ajay.

- I was invited to be part of the SERB Core Research Grant Review team

- Our work on "A Frequency Optimized Linear Scalable Architecture for CNN Inference on FPGAs" by: "Shubhayu Das, Nanditha Rao and Sharad Sinha" was presented at VLSI-D User Design Track (UDT) 2023

- Conducted a 5-day workshop on FPGA/OpenFPGA with VSD

- Gave an invited talk at the ICEE conference, Bangalore on "Performance improvement of machine learning hardware accelerators (inference) on FPGA"

- Co-organized the OpenFPGA tutorial, at FPT'2022: International Conference on Field Programmable Technology, We had nearly 120 registrants. It was a great learning experience to set up machines on the cloud, on Digital Ocean.

Nov 2022:

- Our proposal on "Hardware software co-design to accelerate brain tumour segmentation and classification" was selected in the VLSI-D design contest. A Microchip PolarFire FPGA board is being provided to implement our design and demonstrate it at the conference. Our team consists of 4 MTech students: Vinay, Krishna, Ravi and Ajay. The theme of the design contest was "Hardware and Embedded software co-design with hardware acceleration in an SoC FPGA".

- Two of my iMtech students Sai Manish and Rutvi Padhy are interning at Fachhochschule Kärnten in Villach, Austria. They are working on (1) next-generation photonic highspeed chip-to-chip communication and (2) enabling model-based statistical sign-off of critical analog and RF subsystems. They are working with Prof. Johannes Strum and Prof. Wolfgang Scherr (in collaboration with NXP Semiconductors)

Oct 2022:

- Delivered a KeyNote talk at VSDOpen 2022 online conference

- Invited to be part of SERB Core Research Grant review team

Sep 2022:

.jpg)

- Invited to be part of VLSI-D conference TPC for 2 tracks: Hardware for AI and ML, Low power Digital Architectures

- Presented our work at Indian Institute of Astrophysics Soham Das, Nanditha Rao, D.V.S. Phanindra, Rengaswamy Sridharan "FPGA Accelerated Cross Correlation of Digital Images : Application to Solar Adaptive Optics:, Modern Engineering Trends in Astronomy, Sep 2022

- Signed an MOU with Sensonics Devices Private Limited (SDPL) Rajat Gupta, Sanjay Mehta, Nanditha Rao and Subir Roy through which they will fund an MS(R) student tashish Tiwaru to work on a RISC-V co-processor

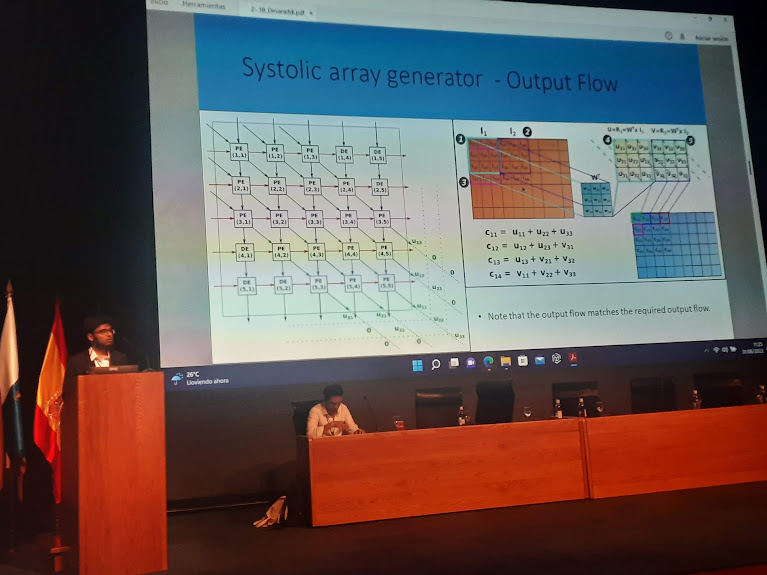

- Our paper was presented in Euromicro Conference on Digital Systems Design 2022. Track: Applications, Architectures, Methods and Tools for Machine – and Deep Learning. Veerendra S Devaraddi and Nanditha Rao, "An FPGA based Tiled Systolic Array Generator to Accelerate CNNs" I was also a session chair for this track

June 2022: Two of my MS(R) students defended their thesis. They are currently placed in Nvidia and Western Digital respectively.

1. Shivani Shah: Cache-accel: FPGA Accelerated Cache Simulator with Partially Reconfigurable Prefetcher

2. Alok Parmar: IMC-Sim: An Architectural Simulator to Benchmark In-Memory Computing in SRAMs (co-advised by Prof. Joycee Mekie, IIT Gandhinagar)

June 2022: Our paper was accepted in Euromicro Conference on Digital Systems Design 2022. Track: Applications, Architectures, Methods and Tools for Machine – and Deep Learning.

Veerendra S Devaraddi and Nanditha Rao, "An FPGA based Tiled Systolic Array Generator to Accelerate CNNs"

June 2022: I conducted a 5-day workshop with VLSI System Design (VSD) on FPGA- Fabric, design and Architecture which covers implementing a RISC-V processor through Xilinx Vivado flow and the OpenFPGA flow (on the Skywater 130nm SOFA eFPGA fabric)

May 2022: Our paper was presented in ISCAS 2022: Alok Parmar, Kailash Prasad, Nanditha Rao, Joycee Mekie, " An Automated Approach to Compare Bit Serial and Bit Parallel In-Memory Computing for DNNs"

Bio:

I completed my PhD from the Department of Electrical Engineering, IIT Bombay, India in 2017 under the supervision of Prof. Madhav Desai. The thesis work focused on studying the impact of single event upsets (soft errors) on digital logic circuits and on FinFET based device layouts. I was awarded the “Institute Organizational Citation” at IIT Bombay. This is awarded to graduating students in recognition of the contribution to institute's organizational activities during the entire stay in the institute.

Prior to joining the PhD programme, I worked as a Hardware design engineer (Signal Integrity) at Intel Technologies, Bangalore for a period of five years. At Intel, I was mainly responsible for signal integrity (SI) simulations of PCIe, LVDS, DisplayPort and HDMI interfaces (entire path from transmitter to package interconnect to motherboard to receiver interconnect). The work involved several motherboard platforms which included processors such as Clarksfield, Sandybridge, Ivybridge and so on. I also reviewed motherboard schematics (laptop segment) of customers and provided design feedback, in addition to developing expertise in IBIS buffer modeling. The work involved cross-geo interactions with Intel Oregon, Penang and Haifa teams. I received 13 Intel ‘spontaneous recognition awards’ and one Intel ‘divisional recognition award’.

My current research interests are in the area of computer architecture and FPGA-based Systems. More specifically the following areas:

- FPGA Acceleration of Neural Networks

- System design using RISC-V based cores

- Exploring FPGA architectures (https://openfpga.readthedocs.io/en/master/overview/motivation/)

- Approximate designs

- Radiation hardened processor cores

- Research Interests

- Honors and Awards

- Selected Publications

- Teaching

- Research & Consulting

- Other Information

FPGA-based accelerators for CNNs, RISC V based designs, FPGA architecture research, Radiation hardened processors, Security aspect of processor design, Cache and prefetcher design

Awards/Funding:

- Financial Grant: SERB SUPRA 2022-2025 (Scientific and Useful Profound Research Advancement)- Rs. 48 lakh.

Objective: SIMD processor versus Systolic arrays for acceleration

Planned Implementation: FPGA prototype and ASIC tapeout (based on Caravel) - Financial Grant: Center for Internet of Ethical Things (CIET), Govt.of Karnataka, 2022-2025:

Submodule: Hardware Security

Objective: Data leakage in a speculative processor in the presence of hardware prefetchers

and its mitigation. -

Microprocessor design challenge 2020 using Shakthi processor

– With Prof. Naveen K, IIT Dharwad and BTech students of IIT Dharwad

– Semi-finalists in the challenge launched by the Govt of India

– Grant: FPGA board and an initial sanction of Rs. 1 lakh - Financial Grant: SERB Core Research Grant (CRG): 2019-2022: Rs. 28 lakh. Completion report

Objective: Microarchitectural techniques to design a secure processor

Implementation: FPGA prototype - Award: MITACS Globalink research award- internship program: $6000

Title of the project: Fault injection framework to study the soft error resilience of FPGA based systems

With Prof. Otmane Ait Mohamed, Concordia university and MS Student: Jhalak Sharma

Implementation: FPGA prototype

Poster summary here

Reviewer:

- IEEE Transactions on Reliability

- VLSI Design Conference

- SERB Core Research Grant (CRG)

Previous Leadership activities/ Recognitions:

-

2017: Awarded the “Institute Organizational Citation”, IIT Bombay. This is awarded to graduating students in recognition of the contribution to institute's organizational activities during the entire stay in the institute.

-

2014-16: Student member of Women’s cell, IIT Bombay. Part of 5 internal complaint committee (ICC) proceedings.

-

2014-16: Member of Student Welfare Society (SWS) committee, IIT Bombay

-

2014-16: Volunteer for conducting the Stem cell donation drive conducted once a year, under the leadership of Prof. Krithi Ramamritham, IIT Bombay.

-

2016: Member of the observing body and penalty committee for Institute student elections, IIT Bombay

-

2014-15: General Secretary - Hostel 11, IIT Bombay - Received “Best Office Bearer” Award in the Hostel 11 council 2014-15

- Shubhayu Das, Nanditha Rao, Sharad Sinha, "A Frequency Optimized Linear Scalable Architecture for CNN Implementation on FPGAs", Design Automation Conference DAC 2023, IP Track presentation

- Shivani Shah, Nanditha P Rao, "MCSim: A Multi-Core Cache Simulator accelerated on a resource-constrained FPGA", GLSVLSI 2023

- Archie Mishra, Nanditha Rao, "DSEAdd: FPGA based Design Space Exploration for Approximate Adders with Variable Bit-precision", ISQED 2023

- Veerendra S Devaraddi and Nanditha Rao, "An FPGA based Tiled Systolic Array Generator to Accelerate CNNs", Euromicro Conference on Digital Systems Design 2022 . Track: Applications, Architectures, Methods and Tools for Machine – and Deep Learning, Aug 2022

- Jhalak Sharma, Nanditha Rao, "The Characterization of Errors in an FPGA-Based RISC-V Processor Due to Single Event Transients", Elsevier, Microelectronics Journal, 2022, Manuscript Number: MEJ-D-21-00709R2

- Alok Parmar, Kailash Prasad, Nanditha Rao, Joycee Mekie, " An Automated Approach to Compare Bit Serial and Bit Parallel In-Memory Computing for DNNs", IEEE International Symposium on Circuits and Systems (ISCAS 2022)

- Alok Parmar, Kailash Prasad, Nanditha Rao, Joycee Mekie, "FastMem: A Fast Architecture-aware Memory Layout Design", International Symposium on Quality Electronic Design (ISQED'22)

- Risikesh R k, Sharad Sinha and Nanditha Rao, ''Variable Bit-Precision Vector Extension for RISC-V Based Processors'', 14th IEEE International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC 2021), Singapore University of Technology and Design, Singapore, December 20-23, 2021

- Shivani Shah, Vaibhavi Mathur, Sahithi Meenakshi Vutakuru, Kavya Borra and Nanditha P. Rao, “Cache-accel: FPGA Accelerated Cache Simulator with Partially Reconfigurable Prefetcher”, EuroMicro Digital System Design 2021

- Prashant Mata, Nanditha Rao, "Flush-Reload Attack and its Mitigation on an FPGA Based Compressed Cache Design", 22nd International Symposium on Quality Electronic Design, April 2021 (ISQED'21)

- Shivani Shah, Sahithi Meenakshi Vutakuru, Nanditha Rao, "FPGA Accelerated Parameterized Cache Simulator", 22nd International Symposium on Quality Electronic Design. April 2021 (ISQED'21)

- Kirti Khandelwal, Jurair Hamid Bhat, Soham Das, Nanditha Rao, Phanindra DVS, Rengaswamy Sridharan, "Verilog code for cross-correlation of two images:, Astronomical Society of India, Feb 2021- Accepted for poster presentation

- J. Sharma, N. Rao and O. A. Mohamed, "Fault Injection Controller Based Framework to Characterize Multiple Bit Upsets for FPGA Designs," 2020 IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA), Singapore, 2020, pp. 1-5, doi: 10.1109/IPFA49335.2020.9260845.

- Nanditha Rao, Madhav Desai, “Quantification of the extent of multiple node charge collection in 14nm bulk FinFETs“, at International conference on Modelling, Simulation and Intelligent computing (MOSICOM), Jan 2020, Dubai

- Shreya Joshi, Prashant Mata, Nanditha Rao, “A Dynamic Base Data Compression Technique for the Last-Level Cache” at International conference on Modelling, Simulation and Intelligent computing (MOSICOM), Jan 2020, Dubai and HiPC 2019 Research Symposium

- Jhalak Sharma, Subir Roy, Nanditha Rao, “Fault injection framework to study the soft error resilience of RISC-V cores on the FPGA”, RISC-V-Workshop Zurich, 2019

- Shreya Joshi, Subir Roy, Nanditha Rao, “Cache compression using variable base BDI technique for RISC-V processors”, RISC-V-Workshop Zurich, 2019

- Nanditha Rao, Madhav Desai, “The likelihood of multiple bit-flips due to neutron strikes and its implications on circuit designs”, 26th IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits, Hangzhou, China, 2019

- Nanditha P. Rao, Madhav P. Desai, “Quantification of the likelihood of single event multiple transients in logic circuits in bulk CMOS technology,” Microelectronics Journal, Volume 72, 2018, Pages 86-99

- N. P. Rao and M. P. Desai, "A Detailed Characterization of Errors in Logic Circuits due to Single-Event Transients," Digital System Design (DSD), 2015 Euromicro Conference, Funchal, 2015, pp. 714-721.

- Nanditha P Rao, Shahbaz Sarik and Madhav P Desai,“On the likelihood of multiple bit upsets in logic circuits”, VLSI Design Conference 2014, Mumbai, India.

- Presentation: Reed Nelson, Sara Stille, Nanditha Rao, Steve Hall, Scott Gilbert, Tony Lewis, Tal Israeli, ‘Impact of halogen free stackup on Pcie signaling’ in the PCI-SIG conference in Santaclara

- Presentation: Nanditha Rao, “De-emphasis buffer modeling issues with IBIS”, in the Asian IBIS Summit, Tokyo

- Presentation: Nanditha Rao, Sara Stille, “Signal integrity challenges and design practices on a mobile platform” in the PCI-SIG conference in Munich

- T. N. Ruckmongathan, Nanditha Rao P., and Ankita Prasad, “Wavelets for Displaying Gray Shades in LCDs”, SID (Society of Information Display) Symposium Digest of Technical Papers, Volume 36, Issue 1, pp. 168-171

VL803- Processor architecture - iMTech/MTech elective

- Review of pipelining and hazards

- Memory hierarchy and branch predictors

- Instruction level parallelism, multiple issue processors, Register renaming

- Superscalar processors- out of order execution/dynamic scheduling

- Multi-core processors, Multi threading, cache coherence protocols, memory consistency

- Virtual memory, TLBs, TLB+ Cache structures

- Cache compression, side-channel attacks

- Heterogeneous systems, SIMD processor, GPU architecture, TPU architecture

EG 211- Computer architecture - integrated MTech core course

- Computer components, bus interconnections

- Instruction set architecture, addressing modes

- Intro to IAS computer/8086 and peripherals

- Memory, caches

- MIPS architecture, instruction execution, pipelining

- Pipelining hazards, resolving hazards

- Branch prediction

VL504: System design with FPGA - Mtech/iMTech elective

- Review of Verilog programming

- FPGA Architecture

- FPGA programming with Xilinx Vivado- Artix-7 FPGA architecture

- ILA, VIO, Block RAMs, IP blocks

- Intro to Zynq architecture, PL programming through AXI

- High level Synthesis through Vivado

VL822: Physical design with ASICs- co-teaching with Dr. Anand Bariya (Senior VP, OpenFIve) - MTech/iMTech elective

- Synthesis, Timing analysis: Using Cadence Genus

- Implementation (PNR): Using Cadence Innovus

- Partitioning, Floor-planning, Placement and Pin Assignment, Routing

- Clock Network Synthesis & Clock Routing

- Timing Closure, Design Rule Check

- Parasitic Extraction and Simulation

- Rapid Adoption Kits (RAK)- from Cadence- for labs

Research areas:

- Hardware acceleration of Neural Networks through FPGA

- Exploring FPGA architectures (OpenFPGA framework)

- FPGA Based Cache Simulator

- RISC-V based Vector processor/co-processor design

- Cache Side-channel attacks: Hardware implementation

- Impact of Soft errors on FPGA based RISC-V designs

MS(R) Supervision:

Shivani Shah: Cache Simulator. She designed a RISC-V Core available here

Alok Parmar: In-memory compute, CACTI vs OpenRAM Memory studies on timing/power

Graduated in 2021:

MS(R): Jhalak Sharma: Characterization of Errors in an FPGA-Based Design Due to Single Event Transients

Works in Western Digital

MS(R): Prashant Mata: Flush-Reload Attack: Implementation and Mitigation on a Compressed Cache on FPGA

Works in SiFive

iMTech: Risikesh R K: Variable bit-precision vector extension for a RISC-V based processor

Office: 134-C

Extension number: 163

Student's achievements/blogs:

Shivani Shah: Placed in Nvidia

RISC-V Workshop blog: https://shivani-shah269.medium.com/risc-v-in-5-days-aba8789c9ad4

Using TL-Verilog for FPGAs: https://shivani-shah269.medium.com/using-tl-verilog-for-fpgas-901a041b4dd9

Alok Parmar: Western Digital

Jhalak Sharma: Western Digital

Prashant Mata: Placed in SiFive